# TC358774XBG/75XBG

## **DSI2LVDS Low Power Bridge Chip**

TC358774/75XBG Functional Specification Copyright © 2005-2010 MIPI Alliance, Inc. All rights reserved. MIPI Alliance Member Confidential. Page 1 of 154

#### 1 NOTICE OF DISCLAIMER

- 2 The material contained herein is not a license, either expressly or impliedly, to any IPR owned or controlled

- 3 by any of the authors or developers of this material or MIPI. The material contained herein is provided on

- 4 an "AS IS" basis and to the maximum extent permitted by applicable law, this material is provided AS IS

- 5 AND WITH ALL FAULTS, and the authors and developers of this material and MIPI hereby disclaim all

- 6 other warranties and conditions, either express, implied or statutory, including, but not limited to, any (if

- 7 any) implied warranties, duties or conditions of merchantability, of fitness for a particular purpose, of

- 8 accuracy or completeness of responses, of results, of workmanlike effort, of lack of viruses, and of lack of

- 9 negligence.

- 10 All materials contained herein are protected by copyright laws, and may not be reproduced, republished,

- 11 distributed, transmitted, displayed, broadcast or otherwise exploited in any manner without the express

- 12 prior written permission of MIPI Alliance. MIPI, MIPI Alliance and the dotted rainbow arch and all related

- 13 trademarks, tradenames, and other intellectual property are the exclusive property of MIPI Alliance and

- 14 cannot be used without its express prior written permission.

15 ALSO, THERE IS NO WARRANTY OF CONDITION OF TITLE, QUIET ENJOYMENT, QUIET

16 POSSESSION, CORRESPONDENCE TO DESCRIPTION OR NON-INFRINGEMENT WITH REGARD

17 TO THIS MATERIAL OR THE CONTENTS OF THIS DOCUMENT. IN NO EVENT WILL ANY

18 AUTHOR OR DEVELOPER OF THIS MATERIAL OR THE CONTENTS OF THIS DOCUMENT OR

19 MIPI BE LIABLE TO ANY OTHER PARTY FOR THE COST OF PROCURING SUBSTITUTE

20 GOODS OR SERVICES, LOST PROFITS, LOSS OF USE, LOSS OF DATA, OR ANY INCIDENTAL,

21 CONSEQUENTIAL, DIRECT, INDIRECT, OR SPECIAL DAMAGES WHETHER UNDER

22 CONTRACT, TORT, WARRANTY, OR OTHERWISE, ARISING IN ANY WAY OUT OF THIS OR

23 ANY OTHER AGREEMENT, SPECIFICATION OR DOCUMENT RELATING TO THIS MATERIAL,

24 WHETHER OR NOT SUCH PARTY HAD ADVANCE NOTICE OF THE POSSIBILITY OF SUCH

25 DAMAGES.

- 26 Without limiting the generality of this Disclaimer stated above, the user of the contents of this Document is

- 27 further notified that MIPI: (a) does not evaluate, test or verify the accuracy, soundness or credibility of the

- 28 contents of this Document; (b) does not monitor or enforce compliance with the contents of this Document; 29 and (c) does not certify, test, or in any manner investigate products or services or any claims of compliance

- 30 with the contents of this Document. The use or implementation of the contents of this Document may

- 31 involve or require the use of intellectual property rights ("IPR") including (but not limited to) patents,

- 32 patent applications, or copyrights owned by one or more parties, whether or not Members of MIPI. MIPI

- 33 does not make any search or investigation for IPR, nor does MIPI require or request the disclosure of any

- 34 IPR or claims of IPR as respects the contents of this Document or otherwise.

- 35 Questions pertaining to this document, or the terms or conditions of its provision, should be addressed to:

- 36 MIPI Alliance, Inc.

- 37 c/o IEEE-ISTO

- 38 445 Hoes Lane

- 39 Piscataway, NJ 08854

- 40 Attn: Board Secretary

This Notice of Disclaimer applies to all DSI input and processing paths related descriptions throughout this document.

TC358774/75XBG Functional Specification

Page 2 of 154

Copyright © 2005-2010 MIPI Alliance, Inc. All rights reserved. MIPI Alliance Member Confidential.

| HISTORY  |            |                                                                                                                                                                                                                                                                                                                                                                            |

|----------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision | Date       | Note                                                                                                                                                                                                                                                                                                                                                                       |

| Rev 0.1  | 4/18/2012  | Init                                                                                                                                                                                                                                                                                                                                                                       |

| Rev 0.2  | 5/16/2012  | <ol> <li>Change PD pin to STBY pin to reflect its function and changed polarity to<br/>active "low"</li> <li>Add Power State Diagram</li> <li>Updated power on/off sequence</li> <li>Replace Pin GPIO[4] with STBY, not "muxed". No need for register bit<br/>0x0400[7]</li> <li>Reduce 0x0450[VSDelay] field to 10 bit</li> <li>Add DSI debug register, 0x05A8</li> </ol> |

| Rev 0.3  | 5/18/2012  | Typo Corrections<br>Remove GPIO[4] related register bits<br>Update debug register 0x05A8                                                                                                                                                                                                                                                                                   |

| Rev 0.4  | 6/11/2012  | <ol> <li>All the reserved bits in register 0x0450 are defaulted to "0".</li> <li>Updated to match with RTL codes</li> <li>Typo corrections</li> </ol>                                                                                                                                                                                                                      |

| Rev 0.5  | 6/21/2012  | <ol> <li>Typo Correction</li> <li>Remove CLKPOL1/2 bits. Update Register LVCFG and Fig 5-12</li> </ol>                                                                                                                                                                                                                                                                     |

| Rev 0.6  | 7/12/2012  | <ol> <li>Remove fields [13:10] in register I2CTIMCTRL (0x0540)</li> <li>Remove registers DSIStart (0x0204) and DSIBusy (0x0208).</li> </ol>                                                                                                                                                                                                                                |

| Rev 0.7  | 7/17/2012  | <ol> <li>Minimum values in register fields H/VTIM1/2 are '1', not '0'</li> <li>Update clock structure Figure 5-5</li> <li>Remove Modification #8 requirement in Rev 0.0 above</li> </ol>                                                                                                                                                                                   |

| Rev 0.8  | 9/20/2012  | <ol> <li>Change register 0x0230 from R/W to RO</li> <li>Update "RESTRICTIONS ON PRODUCT USE" page</li> <li>Update registers 0x0224</li> <li>Update LVDS IP info</li> </ol>                                                                                                                                                                                                 |

| Rev 0.9  | 10/31/2012 | <ol> <li>Typo Fixed</li> <li>Update LVDS PHY</li> <li>RDATAQ register address corrected to 0x54a</li> <li>Typical Power Consumption updated</li> </ol>                                                                                                                                                                                                                     |

| Rev 1.0  | 01/15/2013 | <ol> <li>Update section 5.2.3.6: using RefClk is option</li> <li>Change max LVDS Clk from 85MHz to 135MHz.</li> </ol>                                                                                                                                                                                                                                                      |

| Rev 1.1  | 02/25/2013 | <ol> <li>Update package info in Chapter 7</li> <li>Update Table 5-3, 10-bit Slave address</li> </ol>                                                                                                                                                                                                                                                                       |

| Rev 1.2  | 02/25/2013 | 1. Remove "Draft" watermark                                                                                                                                                                                                                                                                                                                                                |

| Rev 1.3  | 04/12/2013 | <ol> <li>Remove section 8.3.4 LVDS Transmitter Supply Current</li> <li>Emphasize "don't changes" on certain D-PHY register bits</li> <li>HPW minimum requirement is 8-pixel</li> </ol>                                                                                                                                                                                     |

| Rev 1.4  | 05/29/2013 | Update Footer page                                                                                                                                                                                                                                                                                                                                                         |

HISTORY

TC358774/75XBG Functional Specification

Page 3 of 154

Copyright © 2005-2010 MIPI Alliance, Inc. All rights reserved. MIPI Alliance Member Confidential.

#### REFERENCE

- MIPI D-PHY, "MIPI\_D-PHY\_specification\_v01-00-00, May 14, 2009"

2. MIPI Alliance Specification for DSI version 1.01, Feb 2008

- 3. MIPI Alliance Specification for DPI version 2.0, Sep, 2005

- 4. An Introduction to FPD-Link, AN-1032, Application Note, National Semiconductor 2009

- 5. DS90C383/DS90CF384 LVDS Transmitter 24-Bit FPD Link, Data Sheet, National Semiconductor 2000

- 6. THC63LVD823 Single/Dual Link LVDS Transmitter, Data Sheet, Thine Electronics, 2000-2003.

- 7. SN75LVDS83 FlatLink Transmitter, Data Sheet, Texas Instrument, 1997-2009.

TC358774/75XBG Functional Specification

Copyright © 2005-2010 MIPI Alliance, Inc. All rights reserved. MIPI Alliance Member Confidential.

#### Precautions and Usage Considerations Specific to Application Specific Standard Products and General-Purpose Linear Ics

| 1. 🛽                                         | L CAUT                                                                                | ION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------------------------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Use an<br>case<br>that<br>abn<br>and<br>curr | appropri<br>of over<br>exceed i<br>ormal pu<br>the brea<br>ent in cas                 | iate power supply fuse to ensure that a large current does not continuously flow in<br>current and/or IC failure. The IC will fully break down when used under conditions<br>its absolute maximum ratings, when the wiring is routed improperly or when an<br>lse noise occurs from the wiring or load, causing a large current to continuously flow<br>kdown can lead smoke or ignition. To minimize the effects of the flow of a large<br>se of breakdown, appropriate settings, such as fuse capacity, fusing time and<br>uit location, are required.                                                                                                                  |

|                                              | ciro<br>cui<br>fro<br>pro<br>ads                                                      | rour design includes an inductive load such as a motor coil, incorporate a protection cuit into the design to prevent device malfunction or breakdown caused by the rrent resulting from the inrush current at power ON or the negative current resulting m the back electromotive force at power OFF. For details on how to connect a otection circuit such as a current limiting resistor or back electromotive force sorption diode, refer to individual IC datasheets or the IC databook. IC breakdown ay cause injury, smoke or ignition.                                                                                                                            |

|                                              | su                                                                                    | e a stable power supply with ICs with built-in protection functions. If the power oply is unstable, the protection function may not operate, causing IC breakdown. IC eakdown may cause injury, smoke or ignition.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                              | caj<br>reg<br>If ti<br>coi<br>to a<br>sm<br>pai                                       | refully select external components (such as inputs and negative feedback<br>pacitors) and load components (such as speakers), for example, power amp and<br>gulator.<br>here is a large amount of leakage current such as input or negative feedback<br>indenser, the IC output DC voltage will increase. If this output voltage is connected<br>a speaker with low input withstand voltage, overcurrent or IC failure can cause<br>toke or ignition. (The over current can cause smoke or ignition from the IC itself.) In<br>rticular, please pay attention when using a Bridge Tied Load (BTL) connection type<br>that inputs output DC voltage to a speaker directly. |

| Ov<br>ciru<br>imi<br>De<br>ove<br>me         | er current p<br>cumstances<br>nediately.<br>pending or<br>er current p<br>thod of use | Protection Circuit<br>protection circuits (referred to as current limiter circuits) do not necessarily protect ICs under all<br>s. If the Over current protection circuits operate against the over current, clear the over current status<br>in the method of use and usage conditions, such as exceeding absolute maximum ratings can cause the<br>protection circuit to not operate properly or IC breakdown before operation. In addition, depending on the<br>e and usage conditions, if over current continues to flow for a long time after operation, the IC may<br>t resulting in breakdown.                                                                     |

| Th<br>op<br>De                               | ermal shuto<br>erate again<br>pending or                                              | down Circuit<br>down circuits do not necessarily protect ICs under all circumstances. If the Thermal shutdown circuits<br>ast the over temperature, clear the heat generation status immediately.<br>In the method of use and usage conditions, such as exceeding absolute maximum ratings can cause the<br>own circuit to not operate properly or IC breakdown before operation.                                                                                                                                                                                                                                                                                         |

| W                                            | -                                                                                     | n Design<br>In IC with large current flow such as power amp, regulator or driver, please design the device so that<br>priately radiated, not to exceed the specified junction temperature (T <sub>J</sub> ) at any time and condition. These                                                                                                                                                                                                                                                                                                                                                                                                                              |

TC358774/75XBG Functional Specification

Page 5 of 154

Copyright © 2005-2010 MIPI Alliance, Inc. All rights reserved. MIPI Alliance Member Confidential.

## **Contents**

| HISTORY             | 3                                                           |

|---------------------|-------------------------------------------------------------|

| REFERENCE           | 4                                                           |

| 1                   | INTRODUCTION 11                                             |

| 1.1                 | SCOPE 11                                                    |

| 1.2                 | Purpose 11                                                  |

| 2                   | DEVICE OVERVIEW 12                                          |

| 3                   | FEATURES 13                                                 |

| 4                   | PIN LAYOUT 16                                               |

| 4.1                 | BGA64 PIN-OUT DESCRIPTION 17                                |

| 4.2                 | TC358775 BGA64 Pin Count Summary 18                         |

| 4.3                 | BGA49 PIN-OUT DESCRIPTION 19                                |

| 4.4                 | TC358774 BGA49 Pin Count Summary 20                         |

| 5                   | OPERATIONS 21                                               |

| 5.1                 | Power On 22                                                 |

| 5.2                 | Reset 22                                                    |

| 5.3                 | DSI-RX INTERFACE OPERATION 22                               |

| 5.3.1               | Write and Read Access to Chip Configuration Registers 23    |

| 5.3.2               | Streaming Video 25                                          |

| 5.3.3               | Enter and Exit Chip Sleep Mode 28                           |

| 5.3.4               | Enter and Exit Chip Standby State 29                        |

| 5.3.5               | Control of the I2C Master Interface Port 29                 |

| 5.3.6               | DSI Packet Type Support 33                                  |

| 5.3.7               | Reverse Low Power Transmission 35                           |

| 5.4                 | INITIAL CHIP CONFIGURATION 36                               |

| 5.5                 | VIDEO RELATED OPERATION 36                                  |

| 5.5.1               | Video Timing Generation 36                                  |

| 5.5.2               | Pixel Format Translation 38                                 |

| <i>5.5.3</i><br>5.6 | Magic Square Algorithm 38<br>LVDS-TX INTERFACE OPERATION 39 |

| 5.7                 | I2C MASTER INTERFACE OPERATION 59                           |

| 5.8                 | I2C SLAVE INTERFACE OPERATION 45                            |

| 5.9                 | GPIO 47                                                     |

| 5.10                | Power Management 48                                         |

| 6                   | REGISTERS 50                                                |

| 6.1                 | SUMMARY OF REGISTER ADDRESS 50                              |

| 6.2                 | DSI PHY LAYER REGISTERS 53                                  |

| 6.2.1               | DOW DPHYCONTTX Register 53                                  |

| 6.2.2               | CLW DPHYCONTRX Register 54                                  |

| 6.2.3               | DOW DPHYCONTRX Register 55                                  |

| 6.2.4               | D1W_DPHYCONTRX Register 56                                  |

| 6.2.5               | D2W DPHYCONTRX Register 57                                  |

| 6.2.6               | D3W_DPHYCONTRX Register 58                                  |

| 6.2.7               | COM_DPHYCONTRX Register 59                                  |

TC358774/75XBG Functional Specification

| 6.2.8  | CLW_CNTRL Register 60                               |     |

|--------|-----------------------------------------------------|-----|

| 6.2.9  | DOW_CNTRL Register 60                               |     |

| 6.2.10 | D1W_CNTRL Register 61                               |     |

| 6.2.11 | D2W_CNTRL Register 62                               |     |

| 6.2.12 | D3W_CNTRL Register 62                               |     |

| 6.2.13 | DFT Mode Control Register 64                        |     |

| 6.3    | DSI PPI LAYER REGISTERS 65                          |     |

| 6.3.1  | PPI_STARTPPI Register 65                            |     |

| 6.3.2  | PPI_BUSYPPI Register 65                             |     |

| 6.3.3  | PPI_LINEINITCNT Register 66                         |     |

| 6.3.4  | PPI_LPTXTIMECNT Register 66                         |     |

| 6.3.5  | PPI_LANEENABLE Register 67                          |     |

| 6.3.6  | PPI_TX_RX_TA Register 68                            |     |

| 6.3.7  | PPI_CLS_ATMR Register 69                            |     |

| 6.3.8  | PPI_DOS_ATMR Register 70                            |     |

| 6.3.9  | PPI_D1S_ATMR Register 70                            |     |

| 6.3.10 | PPI_D2S_ATMR Register 71                            |     |

| 6.3.11 | PPI D3S ATMR Register 72                            |     |

| 6.3.12 | PPI_DOS_CLRSIPOCOUNT Register                       | 72  |

| 6.3.13 | PPI_D1S_CLRSIPOCOUNT Register                       | 73  |

| 6.3.14 | PPI_D2S_CLRSIPOCOUNT Register                       | 74  |

| 6.3.15 | PPI D3S CLRSIPOCOUNT Register                       | 74  |

| 6.3.16 | CLS PRE Register 75                                 |     |

| 6.3.17 | DOS_PRE Register 76                                 |     |

| 6.3.18 | D1S PRE Register 77                                 |     |

| 6.3.19 | D2S PRE Register 78                                 |     |

| 6.3.20 | D3S PRE Register 79                                 |     |

| 6.3.21 | CLS PREP Register 80                                |     |

| 6.3.22 | DOS PREP Register 81                                |     |

| 6.3.23 | D1S PREP Register 82                                |     |

| 6.3.24 | D2S PREP Register 83                                |     |

| 6.3.25 | D3S PREP Register 84                                |     |

| 6.3.26 | CLS_ZERO Register 85                                |     |

| 6.3.27 | DOS ZERO Register 86                                |     |

| 6.3.28 | D1S ZERO Register 87                                |     |

| 6.3.29 | D2S_ZERO Register 88                                |     |

| 6.3.30 | D3S_ZERO Register 89                                |     |

| 6.3.31 | PPI CLRFLG Register 90                              |     |

| 6.3.32 | PPI CLRSIPO Register 92                             |     |

| 6.3.33 | HSTIMEOUT Register 94                               |     |

| 6.3.34 | HSTIMEOUTENABLE Register 95                         |     |

| 6.4    | DSI PROTOCOL LAYER REGISTERS 96                     |     |

| 6.4.1  | DSI LANEENABLE Register 96                          |     |

| 6.4.2  | DSI_LANESTATUSO Register 97                         |     |

| 6.4.3  | DSI_LANESTATUS1 Register 97                         |     |

| 6.4.4  | DSI_INTSTATUS Register 98                           |     |

| 6.4.5  | DSI_INTMASK Register 101                            |     |

| 6.4.6  | DSI_INTCLR Register 103                             |     |

| 6.4.7  | DSI_LPTXTO Register 105                             |     |

| 6.5    | DSI_EFTATO REGISTER 105                             |     |

| 6.5.1  | DSI GENERAL REGISTERS 100<br>DSIERRCNT Register 106 |     |

| 6.6    | DSIERRCNT REGISTERS 100                             |     |

| 6.6.1  | Application Layer Control Register                  | 107 |

| 0.0.1  | Application Layer Control Register                  | 107 |

TC358774/75XBG Functional Specification

Page 7 of 154

116

| 6.6.2  | DSI Read Packet Length Register 108                  |

|--------|------------------------------------------------------|

| 6.7    | VIDEO PATH CONFIGURATION REGISTERS 109               |

| 6.7.1  | Video Path Control (VPCTRL) 109                      |

| 6.7.2  | Horizontal Timing Control Register 1 (HTIM1) 111     |

| 6.7.3  | Horizontal Timing Control Register 2 (HTIM2) 112     |

| 6.7.4  | Vertical Timing Control Register 1 (VTIM1) 113       |

| 6.7.5  | Vertical Timing Control Register 2 (VTIM2) 114       |

| 6.7.6  | Video Frame Timing Upload Enable (VFUEN) 115         |

| 6.7.7  | LVDS-TX Mux Input Select Control Register (LVMX0003) |

| 6.8    | LVDS CONFIGURATION REGISTERS 118                     |

| 6.8.1  | LVDS Configuration Register (LVCFG) 118              |

| 6.8.2  | LVDS PHY Register 0 (LVPHY0) 119                     |

| 6.8.3  | LVDS PHY Register 1 (LVPHY1) 122                     |

| 6.9    | System Registers 123                                 |

| 6.9.1  | SYS Status Register 123                              |

| 6.9.2  | SYS Reset Register 125                               |

| 6.10   | GPIO REGISTERS 126                                   |

| 6.10.1 | GPIO Control Register 126                            |

| 6.10.2 | GPIO Output Register 127                             |

| 6.10.3 | GPIO Input Register 128                              |

| 6.11   | I2C REGISTERS 129                                    |

| 6.11.1 | I2C Timing Control and Enable Register 129           |

| 6.11.2 | I2C Master Address Register 130                      |

| 6.11.3 | WDATAQ Register 131                                  |

| 6.11.4 | RDATAQ Register 132                                  |

| 6.12   | CHIP ID/REVISION REGISTERS 133                       |

| 6.12.1 | Chip ID and Revision Register 133                    |

| 6.13   | DEBUG REGISTERS 134                                  |

| 6.13.1 | Debug00 Register 134                                 |

| 6.13.2 | DEBUG01 Register 135                                 |

| 6.13.3 | Debug02 Register 136                                 |

| 7      | PACKAGE 137                                          |

| /      | PACKAGE 137                                          |

| 8      | ELECTRICAL CHARACTERISTICS139                        |

| 8.1    | Absolute Maximum Ratings 139                         |

| 8.2    | RECOMMENDED OPERATING CONDITIONS 140                 |

| 8.3    | DC ELECTRICAL SPECIFICATION 141                      |

| 8.3.1  | Normal CMOS I/Os DC Specifications 141               |

| 8.3.2  | DSI Differential I/Os DC Specifications 141          |

| 8.3.3  | LVDS Transmitter DC Specifications 142               |

| 8.4    | AC CHARACTERISTICS 143                               |

| 8.4.1  | DSI Differential I/Os AC Specifications 143          |

| 8.4.2  | LVDS Transmitter AC Specifications 144               |

| 8.4.3  | EXTCLK Clock Input Requirements 147                  |

| 8.4.4  | Reset Timing 147                                     |

| 8.4.5  | Power Supply On and Off Sequence 148                 |

| 8.4.6  | I2C Interface Timing 152                             |

|        | TIONS ON PRODUCT USE 154                             |

|        | -                                                    |

## List of Figures

Figure 4-1 TC358775XBG Chip Pin Layout (BGA64 – Top View)......16

TC358774/75XBG Functional Specification

Page 8 of 154

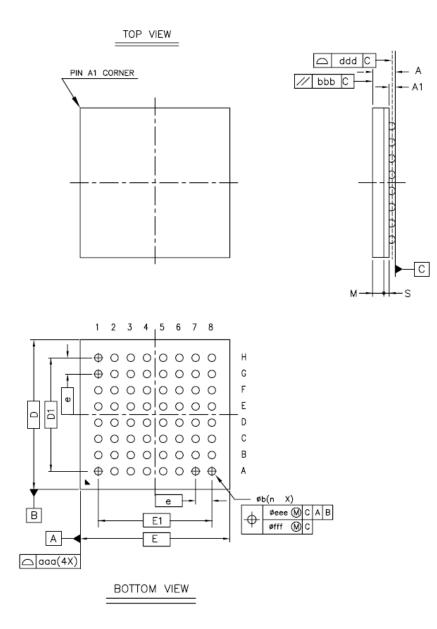

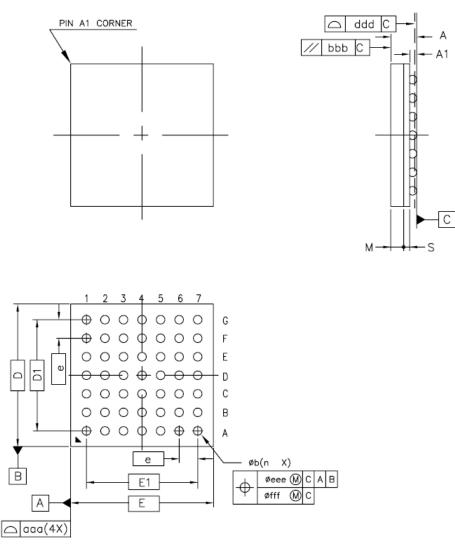

| Figure 4-2 TC358774XBG Chip Pin Layout (BGA49 – Top View)         | 16  |

|-------------------------------------------------------------------|-----|

| Figure 5-1 TC358775XBG Bridge Chip Functional Block Diagram       | 21  |

| Figure 5-2 DSI Long Generic Write Packet                          | 24  |

| Figure 5-3 DSI Generic Short Read Request Packet                  | 25  |

| Figure 5-4 DSI Generic Long Read Response packet                  | 25  |

| Figure 5-5 Clock Mode Selection and Clock Sources                 |     |

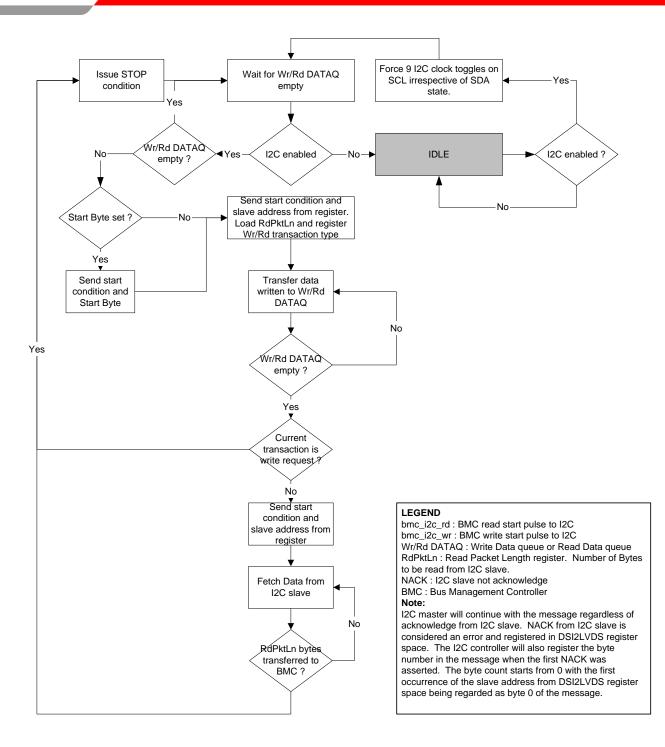

| Figure 5-6 I2C master control flow diagram                        |     |

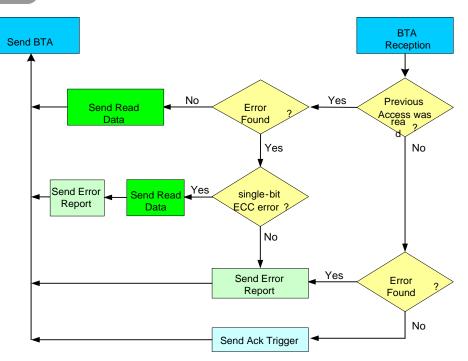

| Figure 5-7 Control Flow of Reverse-Link Transactions              | 36  |

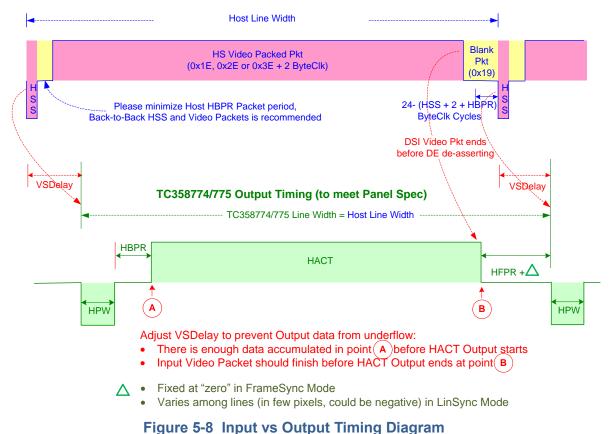

| Figure 5-8 Input vs Output Timing Diagram                         |     |

| Figure 5-9 Magic Square Algorithm Effect                          |     |

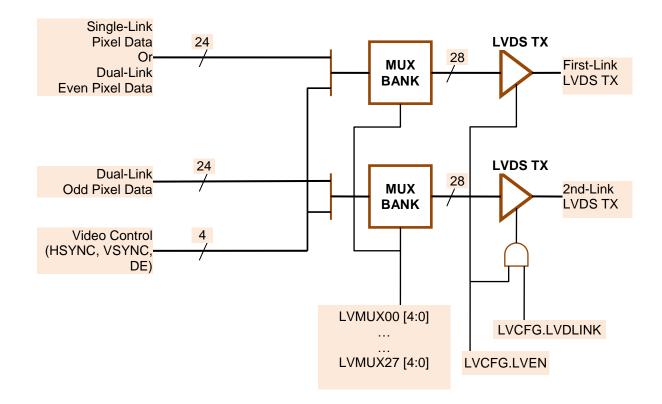

| Figure 5-10 LVDS Link Input Multiplexing Logic                    |     |

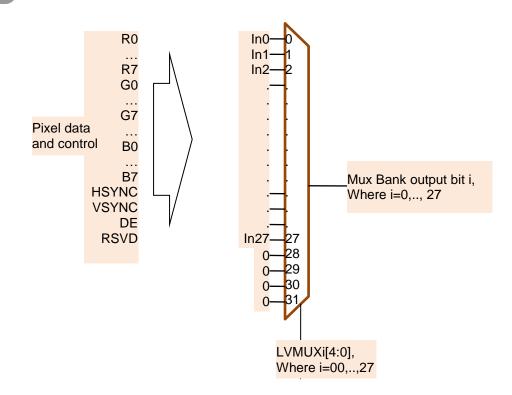

| Figure 5-11 Mux 28-to-1 Connectivity                              | 43  |

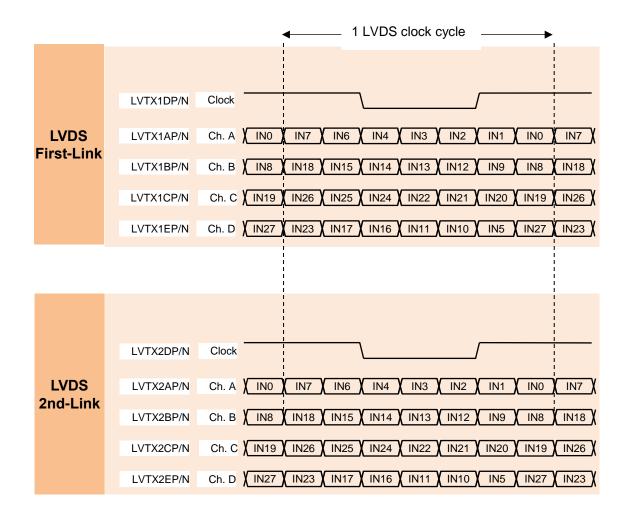

| Figure 5-12 Relationship of Parallel Input Data to LVDS Link      |     |

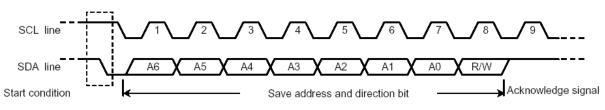

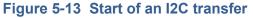

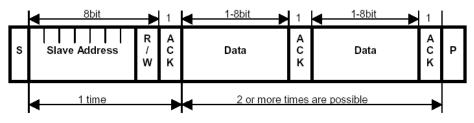

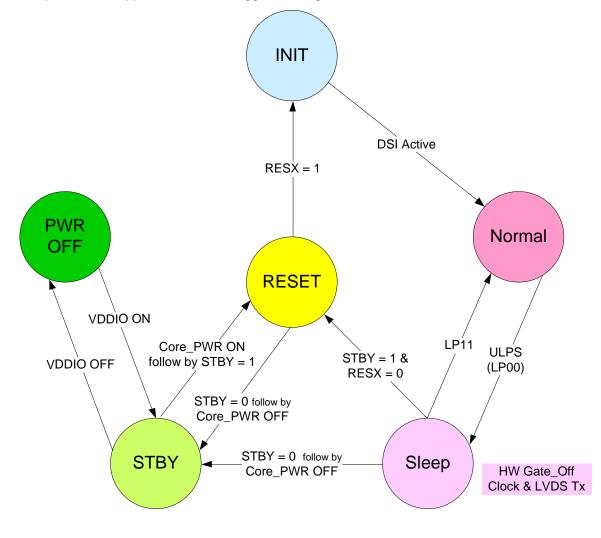

| Figure 5-13 Start of an I2C transfer                              |     |

| Figure 5-14 I2C stop state                                        |     |

| Figure 5-15 I2C data format                                       | 46  |

| Figure 5-16 I2C Slave Write Transaction                           | 47  |

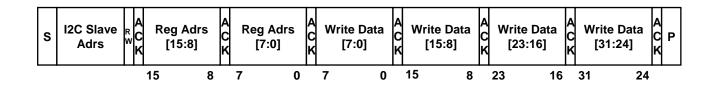

| Figure 5-17 Power State Transition Diagram                        |     |

| Figure 7-1 P-TFBGA64-0606-0.65AZ (TC358775XBG) Package Drawing    |     |

| Figure 7-2 P-TFBGA49-0505-0.65AZ (774XBG) Package Drawing         |     |

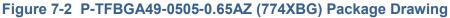

| Figure 8-1 Transmitter Output Transition Timing Diagram           |     |

| Figure 8-2 Input Clock AC Timing Diagram                          |     |

| Figure 8-3 LVDS Output AC Characteristics (Output Eye)            |     |

| Figure 8-4 LVDS Switching Timing Definition                       |     |

| Figure 8-5 EXTCLK Clock Input Timing                              |     |

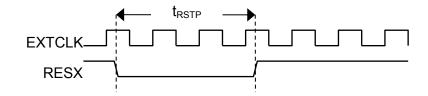

| Figure 8-6 RESET input timing                                     | 147 |

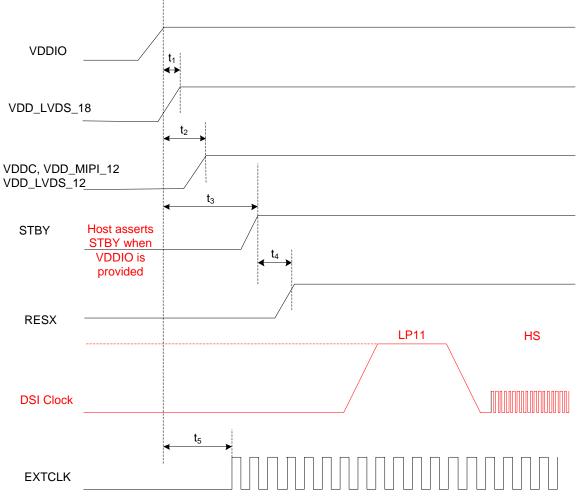

| Figure 8-7 Power-On Sequence Timing                               |     |

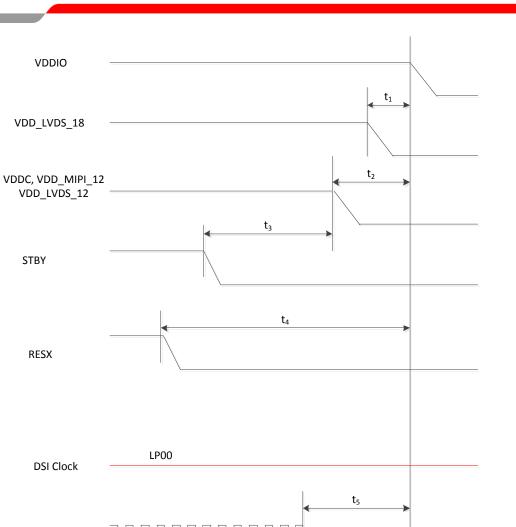

| Figure 8-8 Power-Off Sequence Timing                              |     |

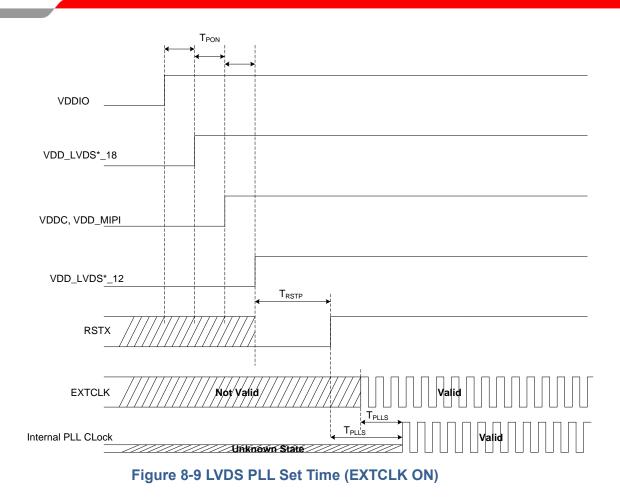

| Figure 8-9 LVDS PLL Set Time (EXTCLK ON)                          |     |

| Figure 8-10 LVDS PLL Set Time (EXTCLK OFF)                        |     |

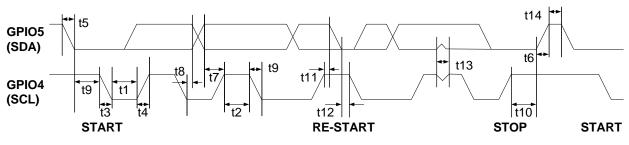

| Figure 8-11 I2C Interface timing                                  | 152 |

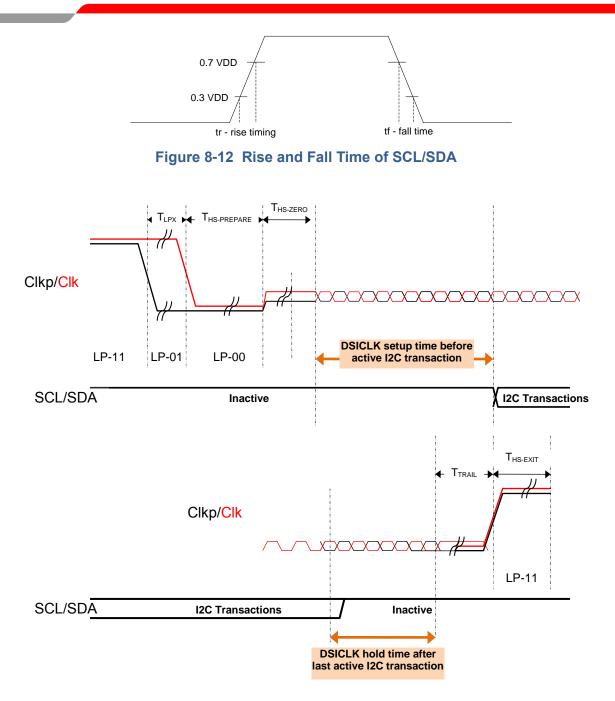

| Figure 8-12 Rise and Fall Time of SCL/SDA                         | 153 |

| Figure 8-13 DSICLK Active Before and After I2C Slave Transactions | 153 |

#### **List of Tables**

| Table 4-1BGA64 Pin Count Summary18Table 4-2BGA49 Pin Count Summary20Table 5-1DSI Packets Pertaining to Video Transmission26Table 5-2I2C controller write message formatting29Table 5-3I2C controller internal I2C read message format33Table 5-4Forward-Link DSI Packet Support34Table 5-5Reverse-Link DSI Packet Support35Table 5-6Pixel Translation Paths38Table 5-7LVDS Single-Link Bit Mapping40Table 5-8LVDS Dual-Link Bit Mapping41Table 5-9Component Power State Summary49Table 7-1Information Summary138Table 8-1Absolute Maximum Ratings139 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C358774/75XBG Functional Specification Page 9 of 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

TC358774/75XBG Functional Specification

| Table 8-2 Recommended Operating Conditions                                | 140 |

|---------------------------------------------------------------------------|-----|

| Table 8-3 Normal CMOS IOs DC Specifications                               | 141 |

| Table 8-4 DSI LP Transmitter DC Specifications                            | 142 |

| Table 8-5 DSI HS Receiver DC Specifications                               | 142 |

| Table 8-6 DSI LP Receiver DC Specifications                               |     |

| Table 8-7 DSI LP Transmitter AC Specifications                            |     |

| Table 8-8 DSI HS Receiver AC Specifications                               | 143 |

| Table 8-9 DSI LP Receiver AC Specifications                               | 144 |

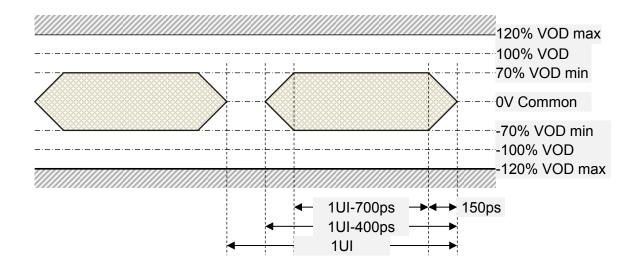

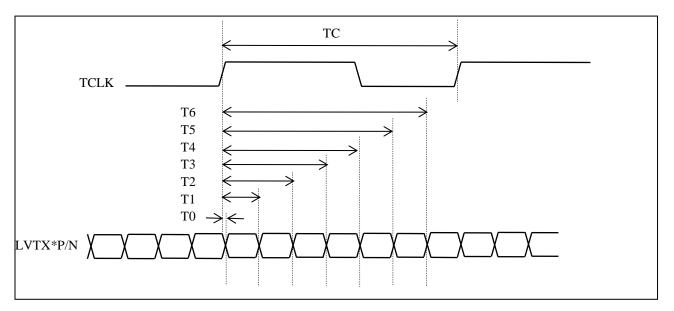

| Table 8-10 LVDS Switching Characteristics (Clock Frequency $\geq$ 50 MHz) |     |

| Table 8-11 LVDS Switching Characteristics (Clock Frequency < 50 MHz)      | 146 |

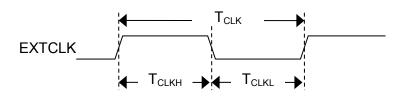

| Table 8-12 EXTCLK Clock Input Requirements                                | 147 |

| Table 8-13 RESET input requirements                                       | 147 |

| Table 8-14 Power-On Sequence Timing                                       |     |

| Table 8-15 Power-Off Sequence Timing                                      |     |

| Table 8-16 LVDS PLL Phase locked loop set time                            |     |

| Table 8-17 I2C Interface Timing                                           |     |

|                                                                           |     |

#### 1 Introduction

The TC358774/75XBG Functional Specification defines operation of the DSI2LVDS low power chip (or more abbreviated, 775XBG chip). 775XBG is the follow-up chip of TC358764/65XBG, which:

- 1. Is pin compatible to TC358764/65XBG

- 2. Exhibit LVDS Tx block operates at 1.8V @135 MHz to reduce operation power

- 3. Update 4-lane DSI Rx max bit rate @ 1 Gbps/lane to support 1920 x 1200 x 24 @60fps

- 4. Add STBY pin with to enable turning on VDDIO power first before other power supplies.

The primary function of this chip is DSI-to-LVDS Bridge, enabling video streaming output over DSI link to drive LVDS-compatible display panels. The chip supports up to 1600x1200 24-bit pixel resolution for single-link LVDS and up to WUXGA (1920x1200 24-bit pixels) resolution for dual-link LVDS. As a secondary function, the chip also supports an I2C Master which is controlled by the DSI link; this may be used as an interface to any other control functions through I2C.

The chip can be configured through the DSI link by sending write register commands through DSI Generic Long Write-packets. It can also be configured through the I2C Slave interface. I2C slave address of 775XBG is 8'b0001\_111X, where X = 0/1 for write/read to/from 775XBG operation.

This specification provides description of two product versions:

- TC358774XBG-49: In BGA49 package, it supports DSI-RX with up to 4 data lanes, and outputs to Single-Link LVDS.

- TC358775XBG-64: In BGA64 package, it supports DSI-RX with up to 4 data lanes, and outputs to Dual-Link LVDS.

#### 1.1 Scope

This document details the operation of the chip, description of each major function that the chip supports, description of the configuration register set, and includes pinout, package, and electrical characteristics information.

#### 1.2 Purpose

This document serves as the vehicle for exchanging detailed technical information of the 775XBG chip and its usage within the target application systems at the customer side. It also serves as the chip functional specification for design implementation and verification.

#### 2 Device Overview

- The 775XBG chip functions primarily as a DSI-to-LVDS communication protocol bridge, enabling video streaming from a Host processor over DSI link to drive LVDS-compatible display panels. In other words, the chip receives video stream input through its DSI receiver (DSI-RX), buffers the received pixel data in a buffer, and then re-transmits the video stream out through the LVDS transmitter.

- As a secondary function, the chip also ports an I2C Master which is controlled by the DSI link; this may be used as a programming interface to other peripherals in the system.

- The chip is configured through the DSI link. Alternatively, it can optionally be configured through the I2C Slave interface; in such case, the I2C Master function would be disabled.

- The reference video pixel clock for the LVDS link is sourced either from an external clock via input pin EXTCLK or derived from DSICLK. The chip integrates a PLL which synthesizes the high-speed clock for use solely to serialize video data over the LVDS link.

- The DSI-RX receiver supports from 1- to 4-Lane configurations at bit rate up to 1 Gbps per lane. Host can transmit video in video mode. In video mode, Host controls video timing by sending video frame and line sync events together with video pixel data; video data transmission can be burst or non-burst. Since the chip integrates only 1024-pixel of video buffer, Host still has to take care of transmitting pixel data at appropriate video line time in order to avoid buffer overflow (or underflow).

- The LVDS transmitter supports a clock frequency of up to 135 MHz for either single- or dual-link.

- The chip supports power management to conserve power when its functions are not in use. Host manages the chip's power consumption states by using ULPS signaling over DSI link and/or STBY pin.

## 3 Features

#### DSI Receiver

- o Configurable 1- up to 4-Data-Lane DSI Link with bi-directional support on Data Lane 0

- Maximum bit rate of 1 Gbps/lane

- Video input data formats:

- RGB565 16 bits per pixel

- RGB666 18 bits per pixel

- RGB666 loosely packed 24 bits per pixel

- RGB888 24 bits per pixel.

- Video frame size:

- Up to 1600x1200 24-bit/pixel resolution to single-link LVDS display panel, limited by 135 MHz LVDS speed

- Up to WUXGA resolutions (1920x1200 24-bit pixels) to dual-link LVDS display panel, limited by 4 Gbps DSI link speed

- Supports Video Stream packets for video data transmission.

- Supports generic long packets for accessing the chip's register set

- o Supports the path for Host to control the on-chip I2C Master

#### • LVDS FPD Link Transmitter

- Supports single-link or dual-link

- Maximum pixel clock frequency of 135 Mhz.

- Maximum pixel clock speed of 135 MHz for single-link or 270 MHz for dual-link

- Supports display up to 1600x1200 24-bit/pixel resolution for single-link, or up to 1920x1200 24-bit resolutions for dual-link

- Supports the following pixel formats:

- RGB666 18 bits per pixel

- RGB888 24 bits per pixel.

- Features Toshiba Magic Square algorithm which enables a RGB666 display panel to produce a display quality equivalent to that of an RGB888 24-bit panel

- o Flexible mapping of parallel data input bit ordering

- Supports programmable clock polarity

- Supports two power saving states

- Sleep state, when receiving DSI ULPS signaling

- Standby state, entered by STBY pin assertion

#### • System Operation

- Host configures the chip through DSI link

- Through DSI link, Host accesses the chip register set using Generic Write and Read packets. One Generic Long Write packet can write to multiple contiguous register addresses

- Includes an I2C Master function which is controlled by Host through DSI link (multimaster is not supported)

- Power management features to save power

- o Configuration registers is also accessible through I2C Slave interface

- Clock Source

- o LVDS pixel clock source is either from external clock EXTCLK or derived from DSICLK.

- A built-in PLL generates the high-speed LVDS serializing clock requiring no external components

#### • Digital Input/Output Signals

- All Digital Input signals are 3.3V tolerant

- All Digital Output signals can output ranging from 1.8V to 3.3V depending on IO supply voltage

#### • Power supply

- MIPI DSI D-PHY: 1.2 V

- LVDS PHY: 1.8 V

- I/O: 1.8 V 3.3V (all IO supply pins must be same level)

- Digital Core: 1.2 V

#### • Power Consumption

- Power Down State is achieved by:

- 1. Reset asserted

- 2. EXTCLK not toggling

- 3. STBY=0

- 4. DSI in ULPS Drive

| Reduced Mode        |       |       |       |         |         |       |      |  |

|---------------------|-------|-------|-------|---------|---------|-------|------|--|

|                     | VDDC  | VDDS  | DSI   | LV      | DS      | TOTAL | Unit |  |

|                     | VDDC  | VDDIO | VDD1  | LVDS1.2 | LVDS1.8 | Power | Unit |  |

|                     | 1.2   | 1.8   | 1.2   | 1.2     | 1.8     |       | V    |  |

| 720x480x18          | 8.60  | 0.11  | 8.40  | 3.60    | 10.00   |       | mA   |  |

| @26 MHz             | 10.32 | 0.20  | 10.08 | 4.32    | 18.00   | 42.92 | mW   |  |

| 1366x768x18         | 17.2  | 0.13  | 14.6  | 8.3     | 11.1    |       | mA   |  |

| @85 MHz             | 20.64 | 0.23  | 17.52 | 9.96    | 19.98   | 68.33 | mW   |  |

| 1920 x 1080x18      | 18.57 | 0.092 | 19.77 | 8.123   | 22.4    |       | mA   |  |

| Dual Link<br>@74MHz | 22.28 | 0.17  | 23.72 | 9.75    | 40.32   | 96.24 | mW   |  |

| Power Down          | 0.03  | 0.01  | 0.02  | 0.01    | 0.02    |       | mA   |  |

| Power Down          | 0.04  | 0.02  | 0.02  | 0.01    | 0.04    | 0.09  | mW   |  |

#### Packaging Information

- o BGA64 (0.65mm ball pitch)

- Supports DSI-RX 4-data-lanes + Dual-Link LVDS-TX

- 6.0mm x 6.0mm x 1.2mm

- o BGA49 (0.65mm ball pitch)

- Supports DSI-RX 4-data-lanes + Single-Link LVDS-TX

- 5.0mm x 5.0mm x 1.2mm

## 4 Pin Layout

| A1           | A2      | A3         | <b>A</b> 4 | A5           | A6           | A7           | <b>A8</b>    |

|--------------|---------|------------|------------|--------------|--------------|--------------|--------------|

| VSS_LVDS2_12 | LVTX2AN | LVTX2BN    | LVTX2CN    | LVTX2DN      | LVTX2EN      | VSS_LVDS2_18 | VSS_LVDS1_12 |

| B1           | B2      | <b>B</b> 3 | B4         | B5           | <b>B</b> 6   | B7           | <b>B</b> 8   |

| VDD_LVDS2_12 | LVTX2AP | LVTX2BP    | LVTX2CP    | LVTX2DP      | LVTX2EP      | VDD_LVDS2_18 | VDD_LVDS1_12 |

| C1           | C2      | C3         | C4         | C5           | C6           | C7           | C8           |

| VSSIO        | VDDIO   | STBY       | GPIO3      | VDD_LVDS2_18 | VSS_LVDS2_18 | LVTX1AP      | LVTX1AN      |

| D1           | D2      | D3         | D4         | D5           | D6           | D7           | D8           |

| EXTCLK       | GPIO2   | GPIO1      | RESX       | ТМ           | VDD_LVDS1_18 | LVTX1BP      | LVTX1BN      |

| E1           | E2      | E3         | E4         | E5           | E6           | E7           | E8           |

| VSSC         | VDDC    | GPIO0      | VDDC       | VSSC         | VSS_LVDS1_18 | LVTX1CP      | LVTX1CN      |

| F1           | F2      | F3         | F4         | F5           | F6           | F7           | F8           |

| VSSIO        | VDDIO   | VDD_MIPI   | VSS_MIPI   | VSS_MIPI     | VDD_MIPI     | LVTX1DP      | LVTX1DN      |

| G1           | G2      | G3         | G4         | G5           | G6           | G7           | G8           |

| I2C_SCL      | DSRXD0P | DSRXD1P    | DSRXCP     | DSRXD2P      | DSRXD3P      | LVTX1EP      | LVTX1EN      |

| H1           | H2      | H3         | H4         | H5           | H6           | H7           | H8           |

| I2C_SDA      | DSRXD0M | DSRXD1M    | DSRXCM     | DSRXD2M      | DSRXD3M      | VDD_LVDS1_18 | VSS_LVDS1_18 |

Figure 4-1 TC358775XBG Chip Pin Layout (BGA64 – Top View)

| A1      | A2      | <b>A3</b>  | <b>A</b> 4 | A5           | <b>A</b> 6   | A7           |

|---------|---------|------------|------------|--------------|--------------|--------------|

| VSSIO   | VDDIO   | RESX       | GPIO0      | VSSC         | VDDC         | VSSC         |

| B1      | B2      | <b>B</b> 3 | B4         | B5           | <b>B6</b>    | B7           |

| EXTCLK  | VDDC    | VSSC       | ТМ         | VDD_LVDS1_12 | LVTX1AP      | LVTX1AN      |

| C1      | C2      | C3         | C4         | C5           | C6           | C7           |

| I2C_SDA | GPIO3   | GPIO2      | GPIO1      | VSS_LVDS1_12 | LVTX1BP      | LVTX1BN      |

| D1      | D2      | D3         | D4         | D5           | D6           | D7           |

| I2C_SCL | STBY    | VSS_MIPI   | VDD_MIPI   | VSS_LVDS1_18 | LVTX1CP      | LVTX1CN      |

| E1      | E2      | E3         | E4         | E5           | E6           | E7           |

| VDDIO   | VSSIO   | VSS_MIPI   | VDD_MIPI   | VDD_LVDS1_18 | LVTX1DP      | LVTX1DN      |

| F1      | F2      | F3         | F4         | F5           | F6           | F7           |

| DSRXD0P | DSRXD1P | DSRXCP     | DSRXD2P    | DSRXD3P      | LVTX1EP      | LVTX1EN      |

| G1      | G2      | G3         | G4         | G5           | G6           | G7           |

| DSRXD0M | DSRXD1M | DSRXCM     | DSRXD2M    | DSRXD3M      | VDD_LVDS1_18 | VSS_LVDS1_18 |

Figure 4-2 TC358774XBG Chip Pin Layout (BGA49 – Top View)

## 4.1 BGA64 Pin-out Description

| Group         | Pin Name      | Ю Туре          | Pin Cnt. | Description                                        | Power<br>Supply<br>Voltage |

|---------------|---------------|-----------------|----------|----------------------------------------------------|----------------------------|

|               | DSICP         | DSI-PHY         | 1        | DSI clock signal - positive                        | 1.2 V                      |

|               | DSICM         | DSI-PHY         | 1        | DSI clock signal - negative                        | 1.2 V                      |

|               | DSIDP[3:0]    | DSI-PHY         | 4        | DSI data lane - positive                           | 1.2 V                      |

| DSI RX IF     | DSIDM[3:0]    | DSI-PHY         | 4        | DSI data lane - negative                           | 1.2 V                      |

|               | VDD_MIPI      | Power           | 2        | MIPI Analog Power Supply                           | 1.2 V                      |

|               | VSS_MIPI      | Ground          | 2        | MIPI Analog Ground                                 | GND                        |

|               | LVTX1AP       | LVDS-PHY        | 1        | LVDS first-link data channel A - positive          | 1.8 V                      |

|               | LVTX1AN       | LVDS-PHY        | 1        | LVDS first-link data channel A - negative          | 1.8 V                      |

|               | LVTX1BP       | LVDS-PHY        | 1        | LVDS first-link data channel B - positive          | 1.8 V                      |

|               | LVTX1BN       | LVDS-PHY        | 1        | LVDS first-link data channel B - negative          | 1.8 V                      |

| -             | LVTX1CP       | LVDS-PHY        | 1        | LVDS first-link data channel C - positive          | 1.8 V                      |

|               | LVTX1CN       | LVDS-PHY        | 1        | LVDS first-link data channel C - negative          | 1.8 V                      |

| First-Link    | LVTX1DP       | LVDS-PHY        | 1        | LVDS first-link data channel D (Clock) - positive  | 1.8 V                      |

| LVDS TX<br>IF | LVTX1DN       | LVDS-PHY        | 1        | LVDS first-link data channel D (Clock) - negative  | 1.8 V                      |

| 1F -          | LVTX1EP       | LVDS-PHY        | 1        | LVDS first-link data channel E - positive          | 1.8 V                      |

|               | LVTX1EN       | LVDS-PHY        | 1        | LVDS first-link data channel E – negative          | 1.8 V                      |

|               | VDD_LVDS1_18  | Power           | 2        | First-link LVDS 1.8V Power Supply                  | 1.8 V                      |

|               | VSS_LVDS1_18  | Ground          | 2        | First-link LVDS 1.8V Ground                        | GND                        |

|               | VDD_LVDS1_12  | Power           | 1        | First-link LVDS 1.2V Power Supply                  | 1.2 V                      |

|               | VSS_LVDS1_12  | Ground          | 1        | First-link LVDS 1.2V Ground                        | GND                        |

|               | LVTX2AP       | LVDS-PHY        | 1        | LVDS second-link data channel A - positive         | 1.8 V                      |

|               | LVTX2AN       | LVDS-PHY        | 1        | LVDS second-link data channel A - negative         | 1.8 V                      |

|               | LVTX2BP       | LVDS-PHY        | 1        | LVDS second-link data channel B - positive         | 1.8 V                      |

|               | LVTX2BN       | LVDS-PHY        | 1        | LVDS second-link data channel B - negative         | 1.8 V                      |

|               | LVTX2CP       | LVDS-PHY        | 1        | LVDS second-link data channel C - positive         | 1.8 V                      |

|               | LVTX2CN       | LVDS-PHY        | 1        | LVDS second-link data channel C - negative         | 1.8 V                      |

| 2nd-Link      | LVTX2DP       | LVDS-PHY        | 1        | LVDS second-link data channel D (Clock) - positive | 1.8 V                      |

| LVDS TX<br>IF | LVTX2DN       | LVDS-PHY        | 1        | LVDS second-link data channel D (Clock) -negative  | 1.8 V                      |

|               | LVTX2EP       | LVDS-PHY        | 1        | LVDS second-link data channel E - positive         | 1.8 V                      |

|               | LVTX2EN       | LVDS-PHY        | 1        | LVDS second-link data channel E – negative         | 1.8 V                      |

|               | VDD_LVDS2_18  | Power           | 2        | Second-link LVDS 1.8V Power Supply                 | 1.8 V                      |

|               | VSS_LVDS2_18  | Ground          | 2        | Second-link LVDS 1.8V Ground                       | GND                        |

|               | VDD_LVDS2_12  | Power           | 1        | Second-link LVDS 1.2V Power Supply                 | 1.2 V                      |

|               | VSS_LVDS2_12  | Ground          | 1        | Second-link LVDS 1.2V Ground                       | GND                        |

|               | I2C_SCL       | S-OD            | 1        | I2C Master or Slave interface clock signal         | 1.8V-3.3V                  |

| I2C IF        | I2C_SDA       | S-OD            | 1        | I2C Master or Slave interface data signal          | 1.8V-3.3V                  |

| GPIO          | <br>GPIO[3:0] | N <sub>PD</sub> | 4        | GPIO bits 3-0                                      | 1.8V-3.3V                  |

| SYSTEM        | RESX          | N               | 1        | Hardware reset, low active                         | 1.8V-3.3V                  |

TC358774/75XBG Functional Specification

Copyright © 2005-2008 MIPI Alliance, Inc. All rights reserved.

Page 17 of 154

| EXTCLK | Ν               | 1 | External pixel clock source | 1.8V-3.3V |

|--------|-----------------|---|-----------------------------|-----------|

| STBY   | Ν               | 1 | Standby pin, low active     | 1.8V-3.3V |

| ТМ     | N <sub>PD</sub> | 1 | Test mode select            | 1.8V-3.3V |

| VDDIO  | Power           | 2 | IO Power Supply             | 1.8-3.3V  |

| VSSIO  | Ground          | 2 | IO Ground                   | GND       |

| VDDC   | Power           | 2 | Digital Core Power Supply   | 1.2 V     |

| VSSC   | Ground          | 2 | Digital Core Ground         | GND       |

#### **Buffer Type Abbreviation:**

| N:                | Normal IO                                |

|-------------------|------------------------------------------|

| N <sub>PD</sub> : | Normal IO with weak Internal Pull-Down   |

| N <sub>PU</sub> : | Normal IO with weak Internal Pull-Up     |

| S-OD:             | Pseudo open-drain output, schmidtt input |

| SCHMIDTT:         | Fail Safe schmidtt input buffer          |

| DSI-PHY:          | front-end analog IO for DSI              |

| LVDS-PHY:         | front-end analog IO for LVDS             |

| A:                | Analog pad                               |

|                   |                                          |

## 4.2 TC358775 BGA64 Pin Count Summary

#### Table 4-1 BGA64 Pin Count Summary

| Group Name      | Pin<br>Count | Notes                       |

|-----------------|--------------|-----------------------------|

| SYSTEM          | 4            |                             |

| DSI-RX IF       | 14           | Include DSI Power & Ground  |

| LVDS-TX IF      | 32           | Include LVDS Power & Ground |

| I2C             | 2            |                             |

| GPIOx           | 4            |                             |

| POWER           | 4            | System Power                |

| GROUND          | 4            | System Ground               |

| Total Pin Count | 64           |                             |

Total Pin Count

TC358774/75XBG Functional Specification

## 4.3 BGA49 Pin-out Description

| Group         | Pin Name     | Ю Туре          | Pin<br>Cnt. | Description                                       | Power<br>Supply<br>Voltage |

|---------------|--------------|-----------------|-------------|---------------------------------------------------|----------------------------|

|               | DSICP        | DSI-PHY         | 1           | DSI clock signal - positive                       | DSICP                      |

|               | DSICM        | DSI-PHY         | 1           | DSI clock signal - negative                       | DSICM                      |

|               | DSIDP[3:0]   | DSI-PHY         | 4           | DSI data lane - positive                          | DSIDP[3:0]                 |

| DSI RX IF     | DSIDM[3:0]   | DSI-PHY         | 4           | DSI data lane - negative                          | DSIDM[3:0]                 |

|               | VDD_MIPI     | Power           | 2           | MIPI Analog Power Supply                          | 1.2 V                      |

|               | VSS_MIPI     | Ground          | 2           | MIPI Analog Ground                                | GND                        |

|               | LVTX1AP      | LVDS-PHY        | 1           | LVDS first-link data channel A - positive         | 1.8 V                      |

|               | LVTX1AN      | LVDS-PHY        | 1           | LVDS first-link data channel A - negative         | 1.8 V                      |

|               | LVTX1BP      | LVDS-PHY        | 1           | LVDS first-link data channel B - positive         | 1.8 V                      |

|               | LVTX1BN      | LVDS-PHY        | 1           | LVDS first-link data channel B - negative         | 1.8 V                      |

|               | LVTX1CP      | LVDS-PHY        | 1           | LVDS first-link data channel C - positive         | 1.8 V                      |

|               | LVTX1CN      | LVDS-PHY        | 1           | LVDS first-link data channel C - negative         | 1.8 V                      |

| First-Link    | LVTX1DP      | LVDS-PHY        | 1           | LVDS first-link data channel D (Clock) - positive | 1.8 V                      |

| LVDS TX<br>IF | LVTX1DN      | LVDS-PHY        | 1           | LVDS first-link data channel D (Clock) - negative | 1.8 V                      |

|               | LVTX1EP      | LVDS-PHY        | 1           | LVDS first-link data channel E - positive         | 1.8 V                      |

|               | LVTX1EN      | LVDS-PHY        | 1           | LVDS first-link data channel E – negative         | 1.8 V                      |

|               | VDD_LVDS1_18 | Power           | 2           | First-link LVDS 1.8V Power Supply                 | 1.8 V                      |

|               | VSS_LVDS1_18 | Ground          | 2           | First-link LVDS 1.8V Ground                       | GND                        |

|               | VDD_LVDS1_12 | Power           | 1           | First-link LVDS 1.2V Power Supply                 | 1.2 V                      |

|               | VSS_LVDS1_12 | Ground          | 1           | First-link LVDS 1.2V Ground                       | GND                        |

|               | I2C_SCL      | S-OD            | 1           | I2C Master or Slave interface clock signal        | 1.8V-3.3V                  |

| I2C IF        | I2C_SDA      | S-OD            | 1           | I2C Master or Slave interface data signal         | 1.8V-3.3V                  |

| GPIO          | GPIO[3:0]    | N <sub>PD</sub> | 4           | GPIO bits 3-0                                     | 1.8V-3.3V                  |

|               | RESX         | N               | 1           | Hardware reset, low active                        | 1.8V-3.3V                  |

|               | EXTCLK       | N               | 1           | External pixel clock source                       | 1.8V-3.3V                  |

|               | STBY         | N               | 1           | Standby pin, low active                           | 1.8V-3.3V                  |

| OVOTEM        | ТМ           | N <sub>PD</sub> | 1           | Test mode select                                  | 1.8V-3.3V                  |

| SYSTEM        | VDDIO        | Power           | 2           | IO Power Supply                                   | 1.8-3.3V                   |

|               | VSSIO        | Ground          | 2           | IO Ground                                         | GND                        |

|               | VDDC         | Power           | 2           | Digital Core Power Supply                         | 1.2 V                      |

|               | VSSC         | Ground          | 3           | Digital Core Ground                               | GND                        |

#### **Buffer Type Abbreviation:**

| N:        | Normal IO                                |

|-----------|------------------------------------------|

| S-OD:     | Pseudo open-drain output, schmidtt input |

| SCHMIDTT: | Fail Safe schmidtt input buffer          |

| DSI-PHY:  | front-end analog IO for DSI              |

| LVDS-PHY: | front-end analog IO for LVDS             |

| A:        | Analog pad                               |

TC358774/75XBG Functional Specification

Copyright © 2005-2008 MIPI Alliance, Inc. All rights reserved.

Page 19 of 154

## 4.4 TC358774 BGA49 Pin Count Summary

#### Table 4-2 BGA49 Pin Count Summary

| Group Name      | Pin<br>Count | Notes                       |

|-----------------|--------------|-----------------------------|

| SYSTEM          | 4            |                             |

| DSI-RX IF       | 14           | Include DSI Power & Ground  |

| LVDS-TX IF      | 16           | Include LVDS Power & Ground |

| I2C             | 2            |                             |

| GPIOx           | 4            |                             |

| POWER           | 4            | System Power                |

| GROUND          | 5            | System Ground               |

| Tatal Dia Osuat | 40           |                             |

Total Pin Count49

### **5** Operations

- The system operation of the 775XBG Bridge Chip is overviewed from the user application point of view in this section.

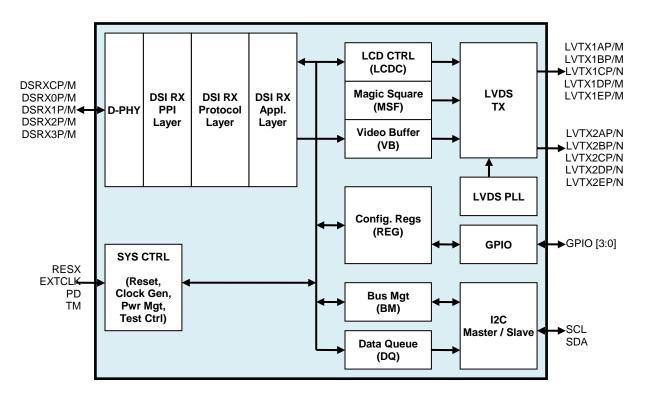

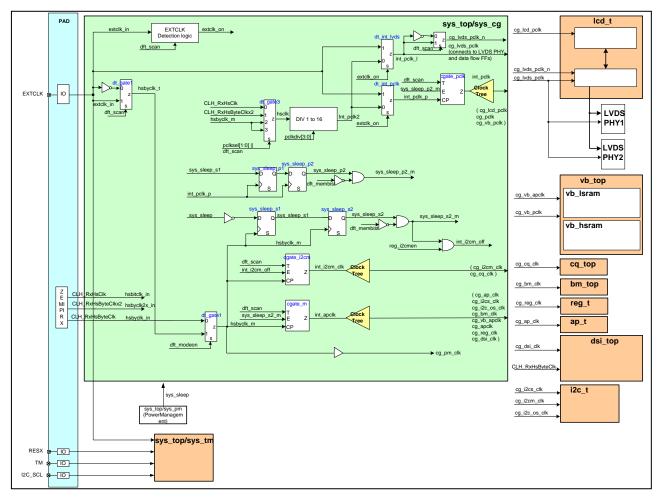

- Following diagram illustrates the functional blocks of the chip and the major data paths interconnecting them.

#### Figure 5-1 TC358775XBG Bridge Chip Functional Block Diagram

- System operation of the chip consists of the following major segments and will be described in that order:

- Power on

- Reset

- Hardware mode selection

- Initial chip configuration

- DSI-RX operation

- Write and read access to the chip configuration and status registers

- Streaming video to LVDS FPD display panels

- Control of the I2C Master Interface port

- Enter and exit chip Sleep state

TC358774/75XBG Functional Specification

Page 21 of 154

TOSHIBA

- Enter and exit chip StandBy state

- DSI packet support

- Reverse low-power transmission

- LVDS-TX operation

- Power management

In this section, description will be limited to system application which is more useful for the system users. These operation segments are implemented by a collection of major functional blocks in the chip as depicted in the functional block diagram above.

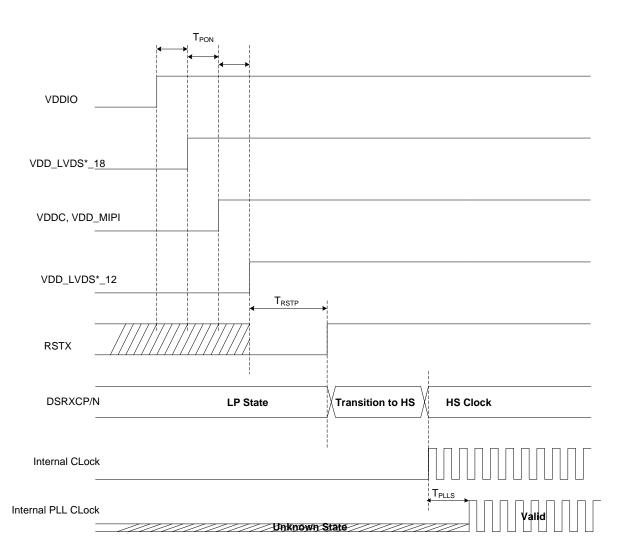

#### 5.1 Power On

The 775XBG Bridge Chip is powered by three supply voltages, 1.2V, 1.8-3.3V and 1.8V, required by different blocks of the chip. If the digital I/Os is powered by 1.8V supply voltage, the number of supply voltages can be reduced to two, 1.2V and 1.8V. Please keep all the input signals at either "Hi-z" or "logic low" state before powering on 775XBG.

The power on/off sequence and input STBY and RESX signals are discussed in section 8.4.5.

After power is applied, the chip input pins should be driven to some deterministic states. Input or bidirectional pins with standard CMOS buffer types should be driven (or weakly pulled) high or low. DSI-RX PHY pins should be driven to LP-11 (stop) state.

#### 5.2 Reset

- 775XBG chip has external hardware reset which distributed to the sub modules inside the 775XBG chip.

- Individual software reset control is also supported for the main functions in the chip. These reset control bits are defined in the SYSRST register.

## 5.3 DSI-RX Interface Operation

- Following reset de-assertion, the chip is ready to receive low-power (LP) mode communication transactions from Host over the DSI link over data lane 0.

- Initial transactions are typically those that write to the chip configuration registers to configure the chip and to activate various functions of the chip.

- Accessing the chip configuration registers can be performed in low-power (LP) mode over only data lane 0, or in high-speed (HS) mode over one or more data lanes.

- Initially, since only data lane 0 is enabled for LP mode reception, DSI-RX configuration registers must be written in LP mode. Then, after DSI-RX is configured and enabled for high-speed reception, subsequent transactions can be in either LP or HS mode.

- The DSI-RX interface is capable of supporting LP mode transactions at data bit rate up to 10 Mbps (lane 0 only) for receive and transmit, and HS mode transactions over one and up to four data lanes, at data bit rate up to 1 Gbps per data lane.

The DSI-RX Interface is used for four purposes:

Write and read access to the chip configuration and status registers

Streaming video to LVDS FPD display panels

Control of the I2C Master Interface port

TC358774/75XBG Functional Specification

Enter and exit chip ultra-low power state (ULPS) or Sleep state

#### 5.3.1 Write and Read Access to Chip Configuration Registers

The 775XBG Bridge Chip makes use of DSI Generic Long packets for Host to write and read to its register set. Format of these packets is defined in the DSI specification. The payload of these packets is further defined here and is specific to the 775XBG Bridge Chip.

#### 5.3.1.1 Write Access

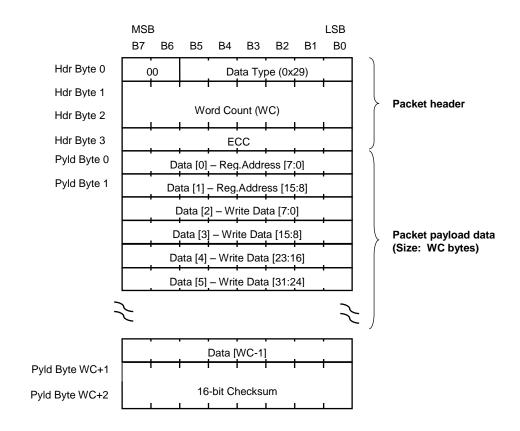

- Host sends a DSI Generic Long Write packet (Data ID = 0x29) over the DSI link for each write access transaction to the chip configuration registers. Payload of this packet is further defined as follows:

- First two bytes of the payload specifies the chip register 16-bit address, hence the address field. The first byte corresponds to address bits [7:0]. The following byte corresponds to address bits [15:8].

- Next four bytes specifies the 32-bit data to be written to the address specified in the address field. The first of the four bytes corresponds to data bits [7:0]; next byte corresponds to data bits [15:8]; ...; last byte corresponds to data bits [31:24].

- "Address auto-increment" capability is supported. That means Host can write to contiguous register address locations with one single packet. The address field specifies the address of the first register to be written to. Each group of following 4 bytes in the payload constitutes the 32-bit data to be written to each of the registers in the group starting with that addressed by the address field.

#### Figure 5-2 DSI Long Generic Write Packet

#### 5.3.1.2 Read Access

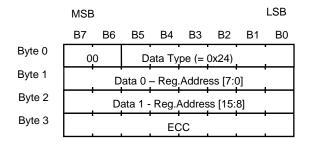

- Host sends a DSI Generic Read packet (Data ID = 0x24) over the DSI link for each read request transaction to the chip configuration registers. Payload of this packet is further defined as follows:

- The two data bytes of the packet specify the chip register 16-bit address, hence the address field. Data byte 0 corresponds to address bits [7:0]. Data byte 1 corresponds to address bits [15:8].

- Immediately after sending this packet, Host performs a Bus-Turn-Around (BTA) sequence to transfer the DSI link ownership to the 775XBG Bridge Chip for it to send a read response packet. (If a BTA does not immediately follow the read request packet, then the read transaction will be abandoned and no read response will be returned.)

The chip detects the BTA sequence and takes one of the following actions:

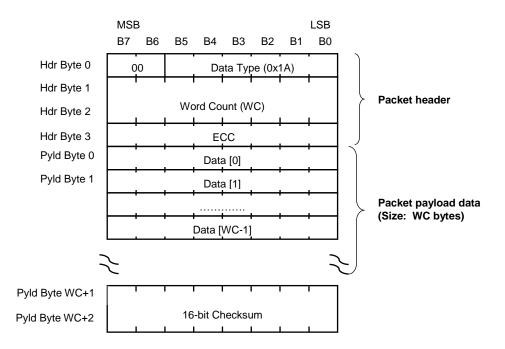

- If the read request packet arrived with no errors (and there are no previously stored errors since the last reverse communication with Host), the chip forms and sends a Generic Long Read Response packet (Data ID = 0x1A) which returns the 4-byte content of the register being addressed (one register access per read)

- If errors are detected during reception of the read request packet (or there are no previously stored errors since the last reverse communication with Host), the chip sends Host an "Acknowledge and Error Report" packet (Data ID = 0x02). Please refer to MIPI DSI Spec. version 1.01 for the details of the error packet.

- If an ECC correctible error in the request was detected and corrected, the chip forms and sends the Generic Long Read Response packet (same as in case 1) followed by the "Acknowledge and Error Report" packet.

- After sending the response, the chip performs its own BTA sequence to give the DSI link ownership back to the Host.

The Generic Short Read Request packet structure is shown in the following figure.

#### Figure 5-3 DSI Generic Short Read Request Packet

#### Figure 5-4 DSI Generic Long Read Response packet

#### 5.3.2 Streaming Video

Video stream from Host over the DSI link will be described in the following context:

- 1. DSI packets for video transmission

- 2. Mode of transmission, video mode only

- 3. Picture resolution and timing parameters

- 4. Pixel format

TC358774/75XBG Functional Specification

Page 25 of 154

- 5. Video data buffering

- 6. DSI clock and display pixel clock

#### 5.3.2.1 DSI Packets for Video Transmission

DSI packets pertaining to video transmission are listed in the following table:

| Data<br>Type | Short/Long<br>Packet | Description                                        | Supported |

|--------------|----------------------|----------------------------------------------------|-----------|

| 6'h01        | Short                | Vsync start                                        | Yes       |

| 6'h11        | Short                | Vsync end                                          | Yes       |

| 6'h21        | Short                | Hsync start                                        | Yes       |

| 6'h31        | Short                | Hsync end                                          | Yes       |

| 6'h09        | Long                 | Null packet                                        | Yes       |

| 6'h19        | Long                 | Blanking Packet                                    | Yes       |

| 6'h0E        | Long                 | Pixel Stream, 16-bit RGB-565 format                | Yes       |

| 6'h1E        | Long                 | Pixel Stream, 18-bit RGB-666 Packed format         | Yes       |

| 6'h2E        | Long                 | Pixel Stream, 18-bit RGB-666 Loosely Packed format | Yes       |

| 6'h3E        | Long                 | Pixel Stream, 24-bit RGB-888 format                | Yes       |

#### Table 5-1 DSI Packets Pertaining to Video Transmission

#### 5.3.2.2 Mode of Transmission

The 775XBG Bridge Chip supports only one mode of video transmission: Video mode.

- In Video mode, Host is expected to transmit all video timing events and pixel data in proper sequence and time. Video timing events are transmitted in these DSI short packets: VSYNC Start (VSS), VSYNC End, HSYNC Start (HSS), and HSYNC End. They must be multiplexed with null (or blank) packets (or transitioned to LP idle cycle) and pixel data packets in the DSI serial link such that their reception at the chip will reflect in signal transition on VSYNC and HSYNC at proper timing for the receiving display panel.

- Pixel data is expected to be transmitted using Pixel Stream packet types (Data Type ID = 0x0E, 0x1E, 0x2E or 0x3E.). Pixel data can be transmitted in non-burst or burst fashion. Non-burst refers to pixel data packet transmission time on DSI link being roughly the same (to account for packet overhead time) as active video line time on LVDS output (i.e. DE = 1). And burst refers to pixel data packet transmission time on DSI link being less than the active video line time on LVDS output.

- Video mode transmission is further differentiated by the types of timing events being transmitted. Video pulse mode refers to the case where both sync start and sync end events (for frame and line) are transmitted. Video event mode refers to the case where only sync start events are transmitted.

- The 775XBG chip operates as event mode only. It ignores VSYNC End and HSYNC End packets. Host is expected to program Hsync and Vsync width in registers HTIM1[HPW] and VTIM1[VPW], respectively.

#### 5.3.2.3 Video Picture Resolution and Timing Parameters

- The maximum display resolution is limited by the data bandwidth available on the LVDS link in single LVDS link case. While it is limited by the data bandwidth available on the DSI link in dual LVDS link case.

- Host is expected to program LVDS timing registers HTIM1/2 and VTIM1/2 before sending video data packets. Host is responsible to control frame/line time with VSS/HSS packets. It is also required to feed video data packets to 775XBG chip in time to prevent data underflow.

- 775XBG chip follows timing parameters set in registers HTIM1/2 and VTIM1/2 to output LVDS stream with panel timing requirement. 775XBG synchronizes its output timing with Host either at frame boundary (VSS) or line boundary (HSS) as programed in register bit VPCTRL[FrameSync]. Please refer to section 5.5.1 for more information.

#### 5.3.2.4 Pixel Format

TOSHIBA

- The chip supports RGB-565, RGB-666 packed or loose, and RGB-888 pixel formats in video data packets received from Host.

- In video mode transmission, pixel format is differentiated by the data type ID in the header of pixel stream packets received.

#### 5.3.2.5 Video Data Buffering

- A Video Line Buffer is provided to buffer the incoming video data due to the speed mismatch between DSI and LVDS links. To a lesser degree, it is also required to absorb the latency caused by deserialization and pipelining along the data path.

- During DSI link speed is slower than that of LVDS link's, data needs to be buffer within 775XBG before outputting to prevent data from underflow. Register field VPCTRL[VSDELAY] is used to for this purpose.

- Pixel data received over the DSI link are always stored in the video line buffer as 24 bits per pixel. Each color component of incoming RGB-565 or packed RGB-666 pixel data is stored as left justified byte.

#### 5.3.2.6 Clock Structure

The 775XBG chip has two clocks source, DSICLK and EXTCLK. The latter is optional.

- DSICLK, or DSI clock, refers to the DSI bit clock used in HS mode transmission of video packets over the DSI link. All video related packets must be transmitted in high-speed mode to ensure the relationships discussed below.

- Either EXTCLK or DSICLK can be used for display pixel clock source, or PCLK. In the case of LVDS Single-Link, PCLK refers to the clock used to transfer one pixel per PCLK period out to the display panel interface and its frequency matches the picture resolution and refresh-timing parameters of the display panel being driven. It is sourced from EXTCLK input pin. For LVDS Dual-Link, two pixels are transmitted to LVDS per PCLK period.

- After reset, If EXTCLK toggles then EXTCLK is selected as pixel clock source, else DSICLK is selected (LVCFG register describes the DSICLK divide options).

- Pixel clock source implies continuous clocking. That means clock pulses must be continuously present during normal operation.

TC358774/75XBG Functional Specification

DSI bit clock must be present when Host issues I2C transactions to the chip even if EXTCLK is present.

Following diagram illustrates the clock source to the internal functional blocks of the chip.

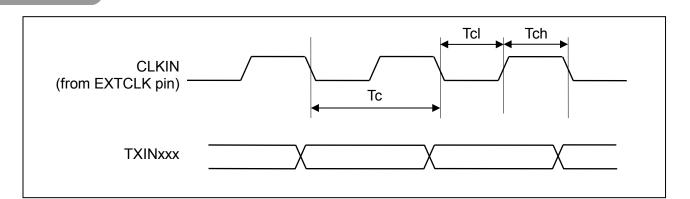

#### Figure 5-5 Clock Mode Selection and Clock Sources

Thus, the 775XBG chip receives video data over the DSI link which is synchronous to DSICLK, and it in turn re-transmits video out to LVDS link which is synchronous to PCLK. In between, the input video data is temporarily held in a 1024-pixel FIFO buffer.

#### 5.3.3 **Enter and Exit Chip Sleep Mode**

- When the display is turned off and the video path from Host to the display panel through 775XBG Bridge Chip is not active, Host sends a ULPS Entry command to instruct the chip to transition into Sleep state. Upon receiving this command, the chip powers down all of its functions except for the DSI low-power receive function which is used to listen to a ULPS Exit command. Subsequently, upon receiving the ULPS Exit command, the chip will exit the ULPS state and transition to standby state.

- No (re-)initialization of 775XBG chip is necessary when exiting Sleep state. 775XBG is ready to transfer data when its PLL/Multiplier is stable.

#### 5.3.4 Enter and Exit Chip Standby State

Host asserts/de-asserts STBY pin to instruct 775XBG goes into/out of StandBy state.

- Before assertion of STBY pin, Host DSI link is recommended to go to LP00/ULPS mode.